Lưu ý: Để tìm hiểu thêm về MIPS có thể tham khảo tại https://vi.wikipedia.org/wiki/MIPS. Trong phạm vi bài viết này, tôi sẽ giới thiệu cho các bạn cách đơn giản nhất để có thể tiếp cận với hợp ngữ.

MIPS là gì?

Theo WIKIPEDIA, MIPS viết tắt của Microprocessor without Interlocked Pipeline Stages, là kiến trúc bộ tập lệnh RISC phát triển bởi MIPS Technologies. Ban đầu kiến trúc MIPS là 32bit, và sau đó là phiên bản 64 bit. Nhiều sửa đổi của MIPS, bao gồm MIPS I, MIPS II, MIPS III, MIPS IV, MIPS V, MIPS32 và MIPS64. Phiên bản hiện tại là MIPS32 và MIPS64.

Cũng có một vài tuỳ chọn mở rộng, bao gồm MIPS-3D có bộ tập lệnh SIMD, MIPS16e thêm khả năng nén vi lệnh để làm chương trình nhỏ hơn và MIPS MT thêm xử lý đa luồng.

Khoá học kiến trúc máy tính ở trường đại học thường tìm hiểu về kiến trúc MIPS. Kiến trúc cực kì ảnh hưởng bởi kiến trúc RISC sau này như là Alpha.

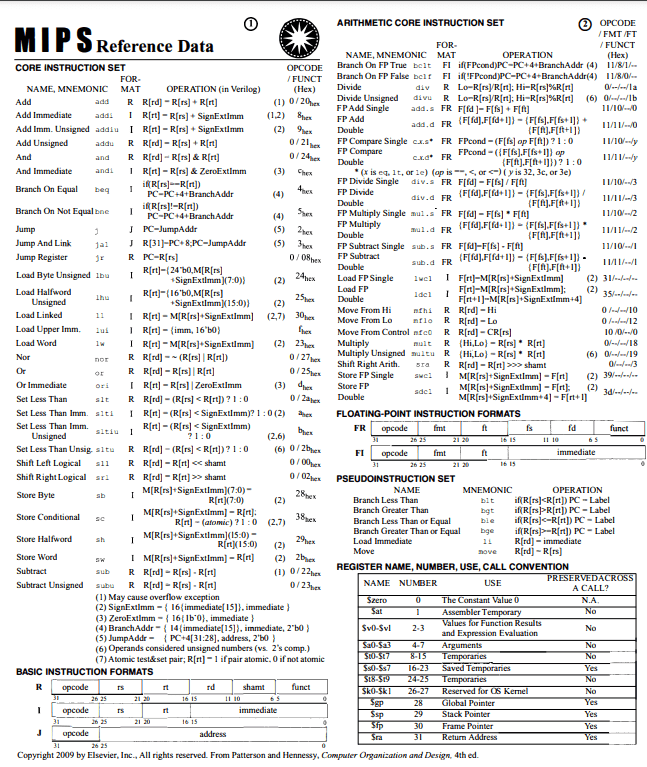

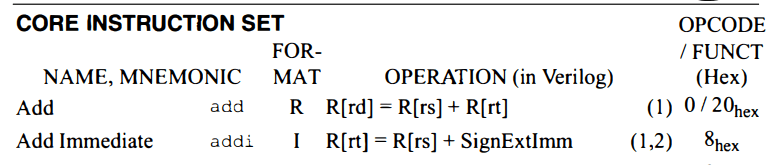

References MIPS

Có thể theo dõi bảng bên dưới đây:

Bản full có thể tìm thấy tại https://inst.eecs.berkeley.edu/~cs61c/resources/MIPS_Green_Sheet.pdf

Chuyển đổi từ hợp ngữ về mã máy

VD: Chuyển đổi đoạn code c++ sau về mã máy:

int a = 0;

a = a + 1;

Các bước thực hiện:

- B1: Viết mã MIPS

- B2: Tra cứu thông tin lệnh theo references table

- B3: Tra cứu cú pháp định dạng và công thức

- B4: Chuyển đổi mã lệnh về mã nhị phân

Cụ thể như sau:

B1: Viết mã MIPS

Đoạn mã để thực thi phép tính bên trên: (Chúng ta sẽ quy định biến a được lưu tại thanh ghi số 8)

#Gán giá trị thanh ghi $8 = $0 + $0 #Thanh ghi $0 có giá trị = 0x0 add $8, $zero, $zero #Gán giá trị thanh ghi $8 = $8 + 1 addi $8, $8, 1

B2: Tra cứu thông tin lệnh theo references table

Ở đoạn code bên trên, tôi đã sử dụng 2 lệnh là add và addi, khi tra cứu bảng references thì ta thấy như sau

add: Lệnh định dạng R Verilog: R[rd] = R[rs] + R[rt] Opcode: 0x00 Funct: 0x20

addi: Lệnh định dạng I Verilog: R[rt] = R[rs] + SignExtImm Opcode: 0x08

B3: Tra cứu cú pháp định dạng và công thức

Định dạng R: 6 bit cao nhất: Opcode 5 bit từ 21-25: địa chỉ của thanh ghi rs 5 bit từ 16-20: địa chỉ của thanh ghi rt 5 bit từ 11-15: địa chỉ của thanh ghi rd 5 bit từ 6-10: 5 bit trường shamt (số bit sẽ dịch trái/phải) 6 bit thấp nhất: trường funct

Định dạng I: 6 bit cao nhất: Opcode 5 bit từ 21-25: địa chỉ của thanh ghi rs 5 bit từ 16-20: địa chỉ của thanh ghi rt 16 bit thấp nhất: trường immediate

Ở định dạng I, ta thấy có trường immediate, còn trong lệnh addi có trường SignExtImm trong mã verilog, dựa vào công thức số (2) ta có thể thấy được trường immediate khi được mở rộng thêm 16 bit bên trái sẽ thành định dạng SignExtImm 32 bit (hay còn gọi là định dạng số mở rộng 32 bit có dấu)

Tất cả thông tin cần thiết đã đủ, việc tiếp theo là…

B4: Chuyển đổi sang mã máy

add $8, $zero, $zero

rd = rs + rt

addi $8, $8, 1

rt = rs + immediate

add $8, $zero, $zero Opcode: 0x00 => BIN: 00 0000 rs: $zero = 0 0000 rt: $zero = 0 0000 rd: $8 = 0 1000 shamt: 0 0000 (Do lệnh add không thực hiện dịch bit) Funct: 0x20 => BIN: 10 0000

Như vậy, lệnh add $8, $zero, $zero khi chuyển sang mã nhị phân sẽ trở thành:00 0000 0 0000 0 0000 0 1000 0 0000 10 0000

Tách theo từng nhóm 4 bit:0000 0000 0000 0000 0100 0000 0010 0000

Chuyển về mã HEX:0x00004020

Tương tự cho lệnh tiếp theo

addi $8, $8, 1 Opcode: 0x08 => BIN: 00 1000 rs: $8 = 0 1000 rt: $8 = 0 1000 imm: 1 = 0000 0000 0000 0001

Như vậy, lệnh addi $8, $8, 1 khi chuyển sang mã nhị phân sẽ trở thành:00 1000 0 1000 0 1000 0000 0000 0000 0001

Tách theo từng nhóm 4 bit:0010 0001 0000 1000 0000 0000 0000 0001

Chuyển về mã HEX:0x21080001

Kết quả kiểm chứng lại với phần mềm MARS:

THE END

One Reply to “Chuyển đổi hợp ngữ MIPS sang mã máy”